Z2: Validation and Demonstrator

Principal Investigators:

Prof. J. Becker, Dr. F. Hannig, Dr. T. Wild

Scientific Researchers:

N. Anantharajaiah, M. Brand, Dr. J. Falk, L. Masing, S. Mahajan, S. Rheindt, A. Srivatsa, É. R. Sousa

Abstract

The major goal of Project Z2 is to provide a common FPGA-based demonstrator environment for validating the principles of invasive computing, including hardware, software, and algorithmic concepts. For this purpose, complete heterogeneous invasive MPSoCs are prototyped, which are essential when simulation-based approaches alone are not able to cope with this enormous complexity or are not accurate enough.

In the first funding phase, a common FPGA-based demonstrator environment was created in order to enable the prototyping of heterogeneous invasive multi-tile MPSoC designs, and thus, debugging and validation of the concepts of invasive computing. The contributions of the different projects across all project areas were integrated into one platform in order to demonstrate the advantages of invasive computing such as improved quality of service, resource utilisation and speed-up of applications. After the establishment of the CRC/Transregio 89, a Synopsys CHIPit Platinum system was purchased, installed and is heavily used at each site (FAU, KIT, TUM) as the validation and demonstration platform. Thanks to its capacity, the system allows for prototyping of multi-million gate designs, and thus, hardware prototypes of novel invasive multicore architectures as investigated in project area B. We developed the necessary components to integrate peripherals like UART, SSRAM, Ethernet and DDR2 Memory into the common demonstrator and established the appropriate tool support for the CHIPit system. In addition to prototyping, the CHIPit platform has shown enormous benefits for co-simulation/emulation and transaction-based verification. In order to ease the debugging of each invasive multi-tile MPSoC design during the integration phase as well as when testing it, we used the above capabilities and built a comprehensive debugging system on top of it. And finally, we gave support to the projects integrating their components into the common demonstrator on the CHIPit.

In the second funding phase, Project Z2 will continue in providing support for demonstrating the benefits of invasive computing across all involved layers, from algorithmic concepts, software and invasive hardware. Project Z2 will establish the generic infrastructure as required for verification and evaluation of any invasive multi-tile architecture by integrating the various HW/SW components from different projects. Special focus will be on supporting the assessment of the major goals of the overall CRC in the second funding phase, such as error resilience (e.g. by methods for fault injection, emulation of error models, see for instance Project B2) and other predictability goals such as security and performance of invasive architectures (see e.g. Project A4, Project B2, Project C5 and Project D1). To support investigating the power efficiency of invasive architectures, power models of the individual components will be emulated and aggregated on the demonstrator platform as well.

Synopsis

The major goal of Project Z2 in the second funding phase of the CRC is also the demonstration of benefits of invasive computing on a real hardware platform, into which contributions from all projects will be integrated. This demonstrator will cover all relevant layers of invasive computing, from the level of hardware to system software and algorithmic concepts of invasive applications. Project Z2 will provide special support to show aspects on the demonstration platform related to the special focal points that are addressed in this funding period:

- predictability/performance guarantees,

- security,

- dependability and

- energy efficiency.

To optimise the integration process of the hardware and software contributions into a common demonstrator, Project Z2 will provide special support for debugging the components and their interaction based on the means offered by the available prototyping platform. In this context, Project Z2 will also provide means for optimised cooperation among the staff members of all CRC projects for testing and verifying components on the demonstrator platform, which has already been started in the first funding phase of the CRC/Transregio.

Special focus will also be given to the visualisation of invasion-specific aspects at system run time to highlight the interaction of the components and the overall system status when invasive applications are executed on the demonstrator.

Finally, we want to realise much larger sized architectures corresponding to the trend towards manycore processor architectures by upgrading the platform to a newest model and FPGA technology.

Approach

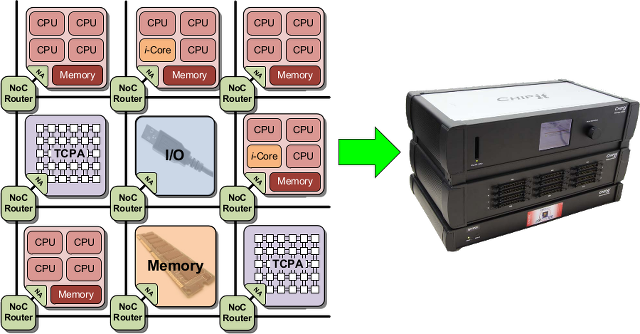

Evaluating architectural innovations is a very time-intensive task. In particular for complex multiprocessor systems like an invasive multi-tile architecture (see e.g. figure below), a robust prototyping platform and run-time debug support is essential.

For this purpose, a CHIPit Platinum from Synopsys, shown right in the figure, was acquired for each of the sites (FAU, KIT and TUM). It contains 6 Virtex5 LX330 FPGAs and allows for the prototyping of multi-million gate designs. In addition, it enables co-simulation/emulation and transaction-based verification.

In cooperation with all projects and the working groups of the CRC, tiled invasive compute architectures, such as the one shown in the above figure on the left, were developed and prototyped for the demonstration of invasive applications from the D projects covering robotics and scientific computing, which make up the common demonstration scenarios. The specified platform consists of standard components and specific hardware or system software contributions by the projects to enable invasive computing.

The left part of the figure above shows an example configuration of an invasive MPSoC: A tiled architecture consisting of RISC-processor–based compute tiles (using LEON3 processor cores or the i-Core as developed from Project B1), compute tiles based on TCPAs (tightly-coupled processor array) as developed in Project B2 as well as I/O and memory tiles. The tiles which contain contributions from all projects of project area B are connected via the iNoC. OctoPOS and iRTSS are running on top of this hardware platform. Within Project Z2, such a heterogeneous hardware architecture, the associated system software and the invasive applications on top were integrated on the CHIPit prototyping system.

Project Z2 contributed in the following three major ways in the realisation of the overall demonstrator:

- Provisioning the basic infrastructure required to realise the common demonstrator on the CHIPit system. This consists of generic hardware components not specific to invasive computing (like common peripherals and controllers) and of the CHIPit-specific tool and design flow support.

- Supporting the integration of the different projects’ contributions, i.e. hardware and software components, into the common demonstrator.

- Coordination work for the definition of demonstrator scenarios on the prototyping system, including milestone planning.

Project Z2 will continue its central role in providing the required support for demonstrating the benefits and properties of invasive computing across all project areas. That is, the demonstration platform not only provides the required testbed for validation for projects from area B from but also for the evaluation of software and algorithmic concepts from project areas C and A, respectively. Project Z2 will provide a generic infrastructure as required for the demonstrator platform as well as coordinate and integrate the various HW/SW components from different projects into a common demonstrator. Compared to the first funding phase, the tasks of Project Z2 will be twofold:

- Project Z2 will maintain the established generic FPGA-based demonstration platform (tools and hardware components for CHIPit) and will allow to easily switch between stable configurations, i.e. architecture variants in order to provide invasive hardware platforms to projects from area C and D from the early beginning of the second funding phase. Similarly, Project Z2 will provide an x86-based mutlicore system (> 64 cores) with an iRTSS port (from Project C1) to all software and application projects. For both FPGA- and x86-based, appropriate (shared) directory structures, version management, remote access and coordination of access will be provided.

- In parallel to the first item, Project Z2 will setup a new FPGA-based platform in order to fulfil the requirements (performance, number of cores, etc.) of the individual projects.

In both parts, Project Z2 will contribute the required support for verification and testing with respect to the major goals of the overall CRC in the second funding phase, which are performance predictability, security, error resilience, and power assessment and energy efficiency.

A comprehensive summary of the major achievements of the first funding phase can be found by accessing Project Z2 first phase website.

Publications

| [1] | Jürgen Becker, Frank Hannig, Thomas Wild, Marcel Brand, Oliver Lenke, and Fabian Lesniak. Validation and demonstrator. In Jürgen Teich, Jörg Henkel, and Andreas Herkersdorf, editors, Invasive Computing, pages 411–431. FAU University Press, August 16, 2022. [ DOI ] |

| [2] | Nidhi Anantharajaiah, Tamim Asfour, Michael Bader, Lars Bauer, Jürgen Becker, Simon Bischof, Marcel Brand, Hans-Joachim Bungartz, Christian Eichler, Khalil Esper, Joachim Falk, Nael Fasfous, Felix Freiling, Andreas Fried, Michael Gerndt, Michael Glaß, Jeferson Gonzalez, Frank Hannig, Christian Heidorn, Jörg Henkel, Andreas Herkersdorf, Benedict Herzog, Jophin John, Timo Hönig, Felix Hundhausen, Heba Khdr, Tobias Langer, Oliver Lenke, Fabian Lesniak, Alexander Lindermayr, Alexandra Listl, Sebastian Maier, Nicole Megow, Marcel Mettler, Daniel Müller-Gritschneder, Hassan Nassar, Fabian Paus, Alexander Pöppl, Behnaz Pourmohseni, Jonas Rabenstein, Phillip Raffeck, Martin Rapp, Santiago Narváez Rivas, Mark Sagi, Franziska Schirrmacher, Ulf Schlichtmann, Florian Schmaus, Wolfgang Schröder-Preikschat, Tobias Schwarzer, Mohammed Bakr Sikal, Bertrand Simon, Gregor Snelting, Jan Spieck, Akshay Srivatsa, Walter Stechele, Jürgen Teich, Furkan Turan, Isaías A. Comprés Ureña, Ingrid Verbauwhede, Dominik Walter, Thomas Wild, Stefan Wildermann, Mario Wille, Michael Witterauf, and Li Zhang. Invasive Computing. FAU University Press, August 16, 2022. [ DOI ] |

| [3] | T. K. R. Arvind, Marcel Brand, Christian Heidorn, Srinivas Boppu, Frank Hannig, and Jürgen Teich. Hardware implementation of hyperbolic tangent activation function for floating point formats. In Proceedings of the 24th International Symposium on VLSI Design and Test (VDAT). IEEE, July 2020. [ DOI ] |

| [4] | Frank Hannig, Javier Navaridas, Dirk Koch, and Ameer Abdelhadi, editors. Proceedings of the 31st IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP). IEEE Computer Society, July 2020. [ DOI ] |

| [5] | Marcel Brand, Michael Witterauf, Alberto Bosio, and Jürgen Teich. Anytime floating-point addition and multiplication – Concepts and implementations. In Proceedings of the 31st IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP), pages 157–164. IEEE, July 2020. [ DOI ] |

| [6] | Sandra Mattauch, Katja Lohmann, Frank Hannig, Daniel Lohmann, and Jürgen Teich. A bibliometric approach for detecting the gender gap in computer science. Communications of the ACM (CACM), 63(5):74–80, May 2020. [ DOI ] |

| [7] | Marcel Brand, Michael Witterauf, Frank Hannig, and Jürgen Teich. Anytime instructions for programmable accuracy floating-point arithmetic. In Proceedings of the ACM International Conference on Computing Frontiers (CF), pages 215–219. ACM, April 2019. [ DOI ] |

| [8] |

Efstathios Sotiriou-Xanthopoulos, Leonard Masing, Sotirios Xydis, Kostas

Siozios, Jürgen Becker, and Dimitrios Soudris.

Opencl-based virtual prototyping and simulation of many-accelerator

architectures.

ACM Trans. Embed. Comput. Syst., 17(5):86:1–86:27, September

2018.

[ DOI ]

Keywords: OpenCL, TLM, co-simulation, distributed memory, fixed-point arithmetic, half-floating-point arithmetic, many-accelerator, memory analysis, parallel architectures, systemC |

| [9] | Éricles R. Sousa, Michael Witterauf, Marcel Brand, Alexandru Tanase, Frank Hannig, and Jürgen Teich. Invasive computing for predictability of multiple non-functional properties: A cyber-physical system case study. In Proceedings of the 29th Annual IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP). IEEE, July 2018. [ DOI ] |

| [10] | Andreas Weichslgartner, Stefan Wildermann, Michael Glaß, and Jürgen Teich. Invasive Computing for Mapping Parallel Programs to Many-Core Architectures. Springer, January 15, 2018. [ DOI ] |

| [11] | Sandra Mattauch, Katja Lohmann, Frank Hannig, Daniel Lohmann, and Jürgen Teich. The gender gap in computer science — A bibliometric analysis, 2018. [ DOI ] |

| [12] | Stephanie Friederich. Automated Hardware Prototyping for 3D Networks on Chips. Dissertation, Institut für Technik der Informationsverarbeitung, Karlsruhe Institute of Technology (KIT), May 23, 2017. |

| [13] | Johny Paul, Walter Stechele, Benjamin Oechslein, Christoph Erhardt, Jens Schedel, Daniel Lohmann, Wolfgang Schröder-Preikschat, Manfred Kröhnert, Tamim Asfour, Éricles R. Sousa, Vahid Lari, Frank Hannig, Jürgen Teich, Artjom Grudnitsky, Lars Bauer, and Jörg Henkel. Resource-awareness on heterogeneous MPSoCs for image processing. Journal of Systems Architecture, 61(10):668–680, November 6, 2015. [ DOI ] |

| [14] | Frank Hannig and Andreas Herkersdorf. Introduction to the special issue on testing, prototyping, and debugging of multi-core architectures. Journal of Systems Architecture, 61(10):600, November 7, 2015. [ DOI ] |

| [15] | Michael Dreschmann, Jan Heisswolf, Michael Geiger, Manuel Haußecker, and Jürgen Becker. A framework for multi-FPGA interconnection using multi gigabit transceivers. In Proceedings of the 28th Symposium on Integrated Circuits and Systems Design (SBCCI), pages 5:1–5:6. ACM, August 2015. [ DOI ] |

| [16] | Johny Paul, Walter Stechele, Éricles R. Sousa, Vahid Lari, Frank Hannig, Jürgen Teich, Manfred Kröhnert, and Tamim Asfour. Self-adaptive harris corner detector on heterogeneous many-core processor. In Proceedings of the Conference on Design and Architectures for Signal and Image Processing (DASIP). IEEE, October 2014. [ DOI ] |

| [17] | Stephanie Friederich, Jan Heisswolf, and Jürgen Becker. Hardware/software debugging of large scale many-core architectures. In Proceedings of the 27th Symposium on Integrated Circuits and Systems Design (SBCCI), pages 1–7. IEEE, September 2014. [ DOI ] |

| [18] | Éricles Sousa, Vahid Lari, Johny Paul, Frank Hannig, Jürgen Teich, and Walter Stechele. Resource-aware computer vision application on heterogeneous multi-tile architecture. Hardware and Software Demo at the University Booth at Design, Automation and Test in Europe (DATE), Dresden, Germany, March 2014. |

| [19] | Stephanie Friederich, Jan Heisswolf, David May, and Jürgen Becker. Hardware prototyping and software debugging of multi-core architectures. In Proceedings of the Synopsys Users Group Conference (SNUG), 2014. |

| [20] | Vahid Lari, Srinivas Boppu, Frank Hannig, Jürgen Teich, and Troy Scott. Hybrid prototyping of tightly-coupled processor arrays for MPSoC designs. Designer Track Poster Presentation at the 50th Design Automation Conference (DAC), Austin, TX, USA, June 2013. |

| [21] | Srinivas Boppu, Vahid Lari, Frank Hannig, and Jürgen Teich. Transactor-based prototyping of heterogeneous multiprocessor system-on-chip architectures. In Proceedings of the Synopsys Users Group Conference (SNUG), May 14, 2013. |

| [22] | Vahid Lari, Srinivas Boppu, Frank Hannig, Shravan Muddasani, Boris Kuzmin, and Jürgen Teich. Resource-aware video processing on tightly-coupled processor arrays. Hardware and Software Demo at the University Booth at Design, Automation and Test in Europe (DATE), Grenoble, France, March 2013. [ .pdf ] |

| [23] | Shravan Muddasani, Srinivas Boppu, Frank Hannig, Boris Kuzmin, Vahid Lari, and Jürgen Teich. A prototype of an invasive tightly-coupled processor array. In Proceedings of the Conference on Design and Architectures for Signal and Image Processing (DASIP), pages 393–394. IEEE, October 2012. |

| [24] | Jürgen Becker, Stephanie Friederich, Jan Heisswolf, Ralf Koenig, and David May. Hardware prototyping of novel invasive multicore architectures. In Proceedings of the 17th Asia and South Pacific Design Automation Conference (ASP-DAC), pages 201–206, January 2012. [ DOI ] |