Z2: Validation and Demonstrator

Principal Investigators:

Prof. Becker, Dr. Hannig, Dr. Wild

Scientific Researchers:

Markus Blocherer, Srinivas Boppu, Joachim Falk, Stephanie Friederich, David May

Abstract

Project Z2 describes the FPGA-based demonstrator platform which will be required a) for early evaluation of invasive hardware, software, and algorithmic concepts, b) reduction of design risks for subsequent ASIC design and development, and c) for prototyping a complete heterogeneous invasive MPSoC as simulation-based approaches alone will not able to cope with this enormous complexity or be not accurate enough.

Synopsis

Often, large scale ASIC designs are prototyped using FPGAs before going into silicon. This is a necessity for the following reasons:

- Early evaluation: An FPGA-based prototyping system is a must for early evaluation of hardware and software concepts of invasive computing. Whereas individual parts might be simulated or prototyped alone, the complex interaction of multiple hardware units and levels of software, however, can only be understood, evaluated and improved on a common demonstrator test bed.

- Prototyping and validation speed-up: In a bottom-up design methodology, individual hardware modules can be functionally verified using simulation tools such as ModelSim from Mentor Graphics, NCsim from Cadence and VCS from Synopsys. This methodology works as long as the design size is limited to just a single processor component. However, RTL simulation will not be possible any more for processor systems including also the complex software for operating system functions and application software. Hence, the above simulation tools are unsuitable for simulating large systems especially when a test case needs to run for a long time. Most of the simulation methods developed in subproject C2 focus on a higher abstraction level in order to explore and validate the concepts of invasive computing, whereas the adequate emulation of a complete MPSoC at register-transfer level may be covered only by a prototyping platform. Prototyping our first invasive MPSoC using FPGA technology is thus a must to provide enough speed and enough accuracy.

- Proof-of-concept: Prototyping also provides a proof-of-functionality in hardware and thus contributes to a safe path to silicon production. Till a few years back, smaller FPGAs were a major obstacle in prototyping large designs. With the advancement in technology, FPGAs have become denser as well as faster. Some high-end FPGAs such as Xilinx Virtex5 LX330 can accommodate about 2 million ASIC gates [1]. Thus, the emulator will be able to prototype not only one component of an InvasIC, but a full complex heterogeneous MPSoC.

- Reduction of design risks: Finally, an FPGA-based prototyping system allows to iteratively make changes to designs of components through reconfiguration of individual parts that may be corrected, refined, or improved with respect to functionality, performance, and area constraints. In all major processor design houses, prototyping is thus a must as changes in silicon and redesigns are often too costly. This reduces design risks for the subsequent ASIC design in the second funding phase enormously.

- Software Co-Development platform for the invasive ASIC: An emulator that allows to map a high gate count is mandatory not only for extensive verification tasks that can be performed tremendously faster than RTL simulation, thus significantly contributing to ASIC risk assessment. In addition, the emulator will be essential for operating system adaptation and driver development for the final invasive MPSoC architecture (the InvasIC), as this task requires fast simulation speed which only emulation can provide.

Approach

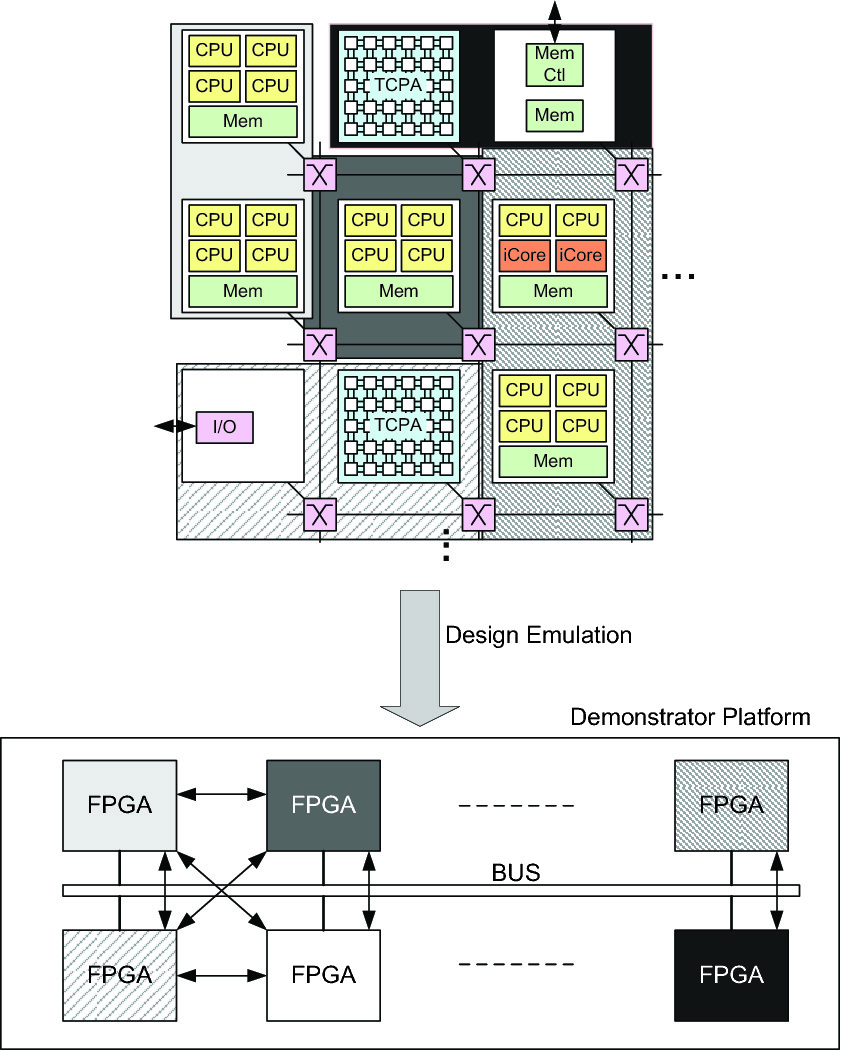

Picture showing an example of an invasive architecture and a possible grouping of different compute tiles and iNOC components onto the FPGA-based demonstrator. The grouping of modules as shown in this figure with different shaded boxes is just for conveying the idea of design partitioning. Synopsys CHIPit system is used as FPGA-based demonstrator.

[1] DS100 Virtex-5 Family Overview,

http://www.xilinx.com/support/documentation/data sheets/ds100.pdf,

2009.

Publications

| [1] | Jürgen Becker, Frank Hannig, Thomas Wild, Marcel Brand, Oliver Lenke, and Fabian Lesniak. Validation and demonstrator. In Jürgen Teich, Jörg Henkel, and Andreas Herkersdorf, editors, Invasive Computing, pages 411–431. FAU University Press, August 16, 2022. [ DOI ] |

| [2] | Nidhi Anantharajaiah, Tamim Asfour, Michael Bader, Lars Bauer, Jürgen Becker, Simon Bischof, Marcel Brand, Hans-Joachim Bungartz, Christian Eichler, Khalil Esper, Joachim Falk, Nael Fasfous, Felix Freiling, Andreas Fried, Michael Gerndt, Michael Glaß, Jeferson Gonzalez, Frank Hannig, Christian Heidorn, Jörg Henkel, Andreas Herkersdorf, Benedict Herzog, Jophin John, Timo Hönig, Felix Hundhausen, Heba Khdr, Tobias Langer, Oliver Lenke, Fabian Lesniak, Alexander Lindermayr, Alexandra Listl, Sebastian Maier, Nicole Megow, Marcel Mettler, Daniel Müller-Gritschneder, Hassan Nassar, Fabian Paus, Alexander Pöppl, Behnaz Pourmohseni, Jonas Rabenstein, Phillip Raffeck, Martin Rapp, Santiago Narváez Rivas, Mark Sagi, Franziska Schirrmacher, Ulf Schlichtmann, Florian Schmaus, Wolfgang Schröder-Preikschat, Tobias Schwarzer, Mohammed Bakr Sikal, Bertrand Simon, Gregor Snelting, Jan Spieck, Akshay Srivatsa, Walter Stechele, Jürgen Teich, Furkan Turan, Isaías A. Comprés Ureña, Ingrid Verbauwhede, Dominik Walter, Thomas Wild, Stefan Wildermann, Mario Wille, Michael Witterauf, and Li Zhang. Invasive Computing. FAU University Press, August 16, 2022. [ DOI ] |

| [3] | T. K. R. Arvind, Marcel Brand, Christian Heidorn, Srinivas Boppu, Frank Hannig, and Jürgen Teich. Hardware implementation of hyperbolic tangent activation function for floating point formats. In Proceedings of the 24th International Symposium on VLSI Design and Test (VDAT). IEEE, July 2020. [ DOI ] |

| [4] | Frank Hannig, Javier Navaridas, Dirk Koch, and Ameer Abdelhadi, editors. Proceedings of the 31st IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP). IEEE Computer Society, July 2020. [ DOI ] |

| [5] | Marcel Brand, Michael Witterauf, Alberto Bosio, and Jürgen Teich. Anytime floating-point addition and multiplication – Concepts and implementations. In Proceedings of the 31st IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP), pages 157–164. IEEE, July 2020. [ DOI ] |

| [6] | Sandra Mattauch, Katja Lohmann, Frank Hannig, Daniel Lohmann, and Jürgen Teich. A bibliometric approach for detecting the gender gap in computer science. Communications of the ACM (CACM), 63(5):74–80, May 2020. [ DOI ] |

| [7] | Marcel Brand, Michael Witterauf, Frank Hannig, and Jürgen Teich. Anytime instructions for programmable accuracy floating-point arithmetic. In Proceedings of the ACM International Conference on Computing Frontiers (CF), pages 215–219. ACM, April 2019. [ DOI ] |

| [8] |

Efstathios Sotiriou-Xanthopoulos, Leonard Masing, Sotirios Xydis, Kostas

Siozios, Jürgen Becker, and Dimitrios Soudris.

Opencl-based virtual prototyping and simulation of many-accelerator

architectures.

ACM Trans. Embed. Comput. Syst., 17(5):86:1–86:27, September

2018.

[ DOI ]

Keywords: OpenCL, TLM, co-simulation, distributed memory, fixed-point arithmetic, half-floating-point arithmetic, many-accelerator, memory analysis, parallel architectures, systemC |

| [9] | Éricles R. Sousa, Michael Witterauf, Marcel Brand, Alexandru Tanase, Frank Hannig, and Jürgen Teich. Invasive computing for predictability of multiple non-functional properties: A cyber-physical system case study. In Proceedings of the 29th Annual IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP). IEEE, July 2018. [ DOI ] |

| [10] | Andreas Weichslgartner, Stefan Wildermann, Michael Glaß, and Jürgen Teich. Invasive Computing for Mapping Parallel Programs to Many-Core Architectures. Springer, January 15, 2018. [ DOI ] |

| [11] | Sandra Mattauch, Katja Lohmann, Frank Hannig, Daniel Lohmann, and Jürgen Teich. The gender gap in computer science — A bibliometric analysis, 2018. [ DOI ] |

| [12] | Stephanie Friederich. Automated Hardware Prototyping for 3D Networks on Chips. Dissertation, Institut für Technik der Informationsverarbeitung, Karlsruhe Institute of Technology (KIT), May 23, 2017. |

| [13] | Johny Paul, Walter Stechele, Benjamin Oechslein, Christoph Erhardt, Jens Schedel, Daniel Lohmann, Wolfgang Schröder-Preikschat, Manfred Kröhnert, Tamim Asfour, Éricles R. Sousa, Vahid Lari, Frank Hannig, Jürgen Teich, Artjom Grudnitsky, Lars Bauer, and Jörg Henkel. Resource-awareness on heterogeneous MPSoCs for image processing. Journal of Systems Architecture, 61(10):668–680, November 6, 2015. [ DOI ] |

| [14] | Frank Hannig and Andreas Herkersdorf. Introduction to the special issue on testing, prototyping, and debugging of multi-core architectures. Journal of Systems Architecture, 61(10):600, November 7, 2015. [ DOI ] |

| [15] | Michael Dreschmann, Jan Heisswolf, Michael Geiger, Manuel Haußecker, and Jürgen Becker. A framework for multi-FPGA interconnection using multi gigabit transceivers. In Proceedings of the 28th Symposium on Integrated Circuits and Systems Design (SBCCI), pages 5:1–5:6. ACM, August 2015. [ DOI ] |

| [16] | Johny Paul, Walter Stechele, Éricles R. Sousa, Vahid Lari, Frank Hannig, Jürgen Teich, Manfred Kröhnert, and Tamim Asfour. Self-adaptive harris corner detector on heterogeneous many-core processor. In Proceedings of the Conference on Design and Architectures for Signal and Image Processing (DASIP). IEEE, October 2014. [ DOI ] |

| [17] | Stephanie Friederich, Jan Heisswolf, and Jürgen Becker. Hardware/software debugging of large scale many-core architectures. In Proceedings of the 27th Symposium on Integrated Circuits and Systems Design (SBCCI), pages 1–7. IEEE, September 2014. [ DOI ] |

| [18] | Éricles Sousa, Vahid Lari, Johny Paul, Frank Hannig, Jürgen Teich, and Walter Stechele. Resource-aware computer vision application on heterogeneous multi-tile architecture. Hardware and Software Demo at the University Booth at Design, Automation and Test in Europe (DATE), Dresden, Germany, March 2014. |

| [19] | Stephanie Friederich, Jan Heisswolf, David May, and Jürgen Becker. Hardware prototyping and software debugging of multi-core architectures. In Proceedings of the Synopsys Users Group Conference (SNUG), 2014. |

| [20] | Vahid Lari, Srinivas Boppu, Frank Hannig, Jürgen Teich, and Troy Scott. Hybrid prototyping of tightly-coupled processor arrays for MPSoC designs. Designer Track Poster Presentation at the 50th Design Automation Conference (DAC), Austin, TX, USA, June 2013. |

| [21] | Srinivas Boppu, Vahid Lari, Frank Hannig, and Jürgen Teich. Transactor-based prototyping of heterogeneous multiprocessor system-on-chip architectures. In Proceedings of the Synopsys Users Group Conference (SNUG), May 14, 2013. |

| [22] | Vahid Lari, Srinivas Boppu, Frank Hannig, Shravan Muddasani, Boris Kuzmin, and Jürgen Teich. Resource-aware video processing on tightly-coupled processor arrays. Hardware and Software Demo at the University Booth at Design, Automation and Test in Europe (DATE), Grenoble, France, March 2013. [ .pdf ] |

| [23] | Shravan Muddasani, Srinivas Boppu, Frank Hannig, Boris Kuzmin, Vahid Lari, and Jürgen Teich. A prototype of an invasive tightly-coupled processor array. In Proceedings of the Conference on Design and Architectures for Signal and Image Processing (DASIP), pages 393–394. IEEE, October 2012. |

| [24] | Jürgen Becker, Stephanie Friederich, Jan Heisswolf, Ralf Koenig, and David May. Hardware prototyping of novel invasive multicore architectures. In Proceedings of the 17th Asia and South Pacific Design Automation Conference (ASP-DAC), pages 201–206, January 2012. [ DOI ] |