B3: Invasive Loosely-Coupled MPSoCs

Principal Investigators:

Prof. Herkersdorf, Prof. Henkel

Scientific Researchers:

Anton Ivanov, Ravi Kumar Pujari, Dr. Muhammad Shafique, Benjamin Vogel, Thomas Wild

Abstract

Principal focus of this subproject is on enabling standard IP-based MPSoC platforms to benefit from the invasive computing and programming paradigm in a power-efficient way. This goal is tackled by introducing a) a fast decentralised hardware mechanism for distributing processing requests among CPU cores according to a policy determined by the run-time support system (iRTSS), and b) a corresponding management policy for operating the invasive platform in compliance with overall power and reliability optimisation targets.

Synopsis

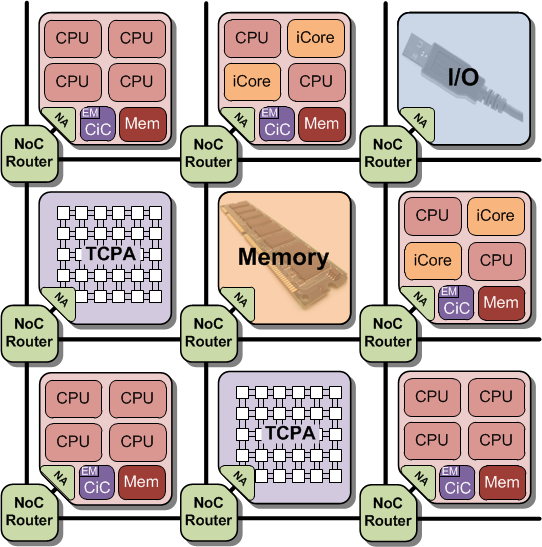

Subproject B3 strives to enable MPSoC platforms consisting of

loosely-coupled standard RISC processors for performance-optimised and

energy-efficient invasive computing. The major research will be on (1)

functional extensions on the hardware level to optimise latency and software

overhead when distributing application threads among processor cores. A further

major contribution will be (2) extensions for providing a low power

infrastructure designed for the resource-aware application paradigm of invasive

computing. Offloading latency-critical tasks from software to dedicated

hardware modules as well as dynamic utilisation management of individual cores

contribute to increased power efficiency of the invasive many-core SoC. To

guarantee consistent operation of the platform, CIC-based distribution of

threads and power gating will be tackled in a coordinated manner. In order to

achieve high processing performance and at the same time optimised power

efficiency the following topics will be investigated:

- In order to optimise invasive programming on standard RISC-based MPSoC platforms, we propose Dynamic Many-Core i-let Controllers (CICs) as macroarchitectural hardware extensions to supplement the software-based iRTSS. CICs assist and accelerate infection of processor cores, that is, the binding of i-lets. The idea is to delegate those functions to CICs that can be implemented with much lower latency and power dissipation in hardware, resulting in higher performance of an invasive MPSoC. Thus, the binding decision will be decentralised and takes local status information into account. This will lead to better scalability in terms of the number of processor cores per chip and higher fault-tolerance. Major scientific goals are to define an appropriate task split and interplay between CICs and the iRTSS, and the optimal representation and execution of rules implementing the policy of the iRTSS to distribute i-lets.

- The introduction of CICs implies additional complexity and hardware overhead. Therefore, the optimisation of the trade off between the associated hardware overhead, and the gain in performance and power efficiency has to be investigated and balanced.

- For the low power infrastructure we plan to implement Virtual Power Gating (ViPG) in which voltage is switched off at the application level. When it is decided that an application is to be gated (based on knowledge from the application design or the iRTSS), ViPG uses data gathered from CICs or the iRTSS to determine which actual hardware components are involved. If the energy saving from ViPG exceeds the required costs, these hardware components are then gated.

Approach

In the tiled architecture, the CiC is envisioned to assign the i-lets to the cores within a tile of loosely-coupled Leon cores or iCores based on constraints given by the application developer. The interconnection between the power management infrastructure and the i-let assignment is fulfilled by the Energy Manager (EM) within the CIC. The power management policy is tailored to the application's needs and is influenced through hints about the expected idle time expressed by the application.

Publications

| [1] | Nidhi Anantharajaiah, Tamim Asfour, Michael Bader, Lars Bauer, Jürgen Becker, Simon Bischof, Marcel Brand, Hans-Joachim Bungartz, Christian Eichler, Khalil Esper, Joachim Falk, Nael Fasfous, Felix Freiling, Andreas Fried, Michael Gerndt, Michael Glaß, Jeferson Gonzalez, Frank Hannig, Christian Heidorn, Jörg Henkel, Andreas Herkersdorf, Benedict Herzog, Jophin John, Timo Hönig, Felix Hundhausen, Heba Khdr, Tobias Langer, Oliver Lenke, Fabian Lesniak, Alexander Lindermayr, Alexandra Listl, Sebastian Maier, Nicole Megow, Marcel Mettler, Daniel Müller-Gritschneder, Hassan Nassar, Fabian Paus, Alexander Pöppl, Behnaz Pourmohseni, Jonas Rabenstein, Phillip Raffeck, Martin Rapp, Santiago Narváez Rivas, Mark Sagi, Franziska Schirrmacher, Ulf Schlichtmann, Florian Schmaus, Wolfgang Schröder-Preikschat, Tobias Schwarzer, Mohammed Bakr Sikal, Bertrand Simon, Gregor Snelting, Jan Spieck, Akshay Srivatsa, Walter Stechele, Jürgen Teich, Furkan Turan, Isaías A. Comprés Ureña, Ingrid Verbauwhede, Dominik Walter, Thomas Wild, Stefan Wildermann, Mario Wille, Michael Witterauf, and Li Zhang. Invasive Computing. FAU University Press, August 16, 2022. [ DOI ] |

| [2] | Marcel Mettler, Martin Rapp, Heba Khdr, Daniel Mueller-Gritschneder, Jörg Henkel, and Ulf Schlichtmann. An fpga-based approach to evaluate thermal and resource management strategies of many-core processors. ACM Trans. Archit. Code Optim., 19(3), may 2022. |

| [3] | Martin Rapp, Hussam Amrouch, Yibo Lin, Bei Yu, David Z Pan, Marilyn Wolf, and Jörg Henkel. MLCAD: A survey of research in machine learning for CAD (keynote paper). IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2022. |

| [4] | Mohammed Bakr Sikal, Heba Khdr, Martin Rapp, and Jörg Henkel. Thermal- and cache-aware resource management based on ML-driven cache contention prediction. In Design, Automation & Test in Europe (DATE). IEEE, 2022. |

| [5] | Martin Rapp, Nikita Krohmer, Heba Khdr, and Jörg Henkel. NPU-accelerated imitation learning for thermal- and QoS-aware optimization of heterogeneous multi-cores. In Design, Automation & Test in Europe (DATE). IEEE, 2022. |

| [6] | Martin Rapp. Machine Learning for Resource-Constrained Computing Systems. Dissertation, Chair of Embedded Systems, Department of Informatics, Karlsruhe Institute of Technology, Germany, 2022. |

| [7] | Martin Rapp, Mohammed Bakr Sikal, Heba Khdr, and Jörg Henkel. SmartBoost: Lightweight ML-driven boosting for thermally-constrained many-core processors. In Design Automation Conference (DAC). ACM/IEEE, 2021. |

| [8] | Mark Sagi, Martin Rapp, Heba Khdr, Yizhe Zhang, Nael Fasfous, Nguyen Anh Vu Doan, Thomas Wild, Jörg Henkel, and Andreas Herkersdorf. Long short-term memory neural network-based power forecasting of multi-core processors. In 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2021. |

| [9] | Heba Khdr, Muhammad Shafique, Santiago Pagani, Andreas Herkersdorf, and Jörg Henkel. Combinatorial auctions for temperature-constrained resource management in manycores. IEEE Transactions on Parallel and Distributed Systems, 31(7):1605–1620, 2020. |

| [10] | Martin Rapp, Anuj Pathania, Tulika Mitra, and Jörg Henkel. Neural network-based performance prediction for task migration on s-nuca many-cores. IEEE Transactions on Computers, 2020. |

| [11] | Martin Rapp, Mark Sagi, Anuj Pathania, Andreas Herkersdorf, and Jörg Henkel. Power- and cache-aware task mapping with dynamic power budgeting for many-cores. IEEE Transactions on Computers, 69(1):1–13, 2020. |

| [12] | Behnaz Pourmohseni, Michael Glaß, Jörg Henkel, Heba Khdr, Martin Rapp, Valentina Richthammer, Tobias Schwarzer, Fedor Smirnov, Jan Spieck, Jürgen Teich, Andreas Weichslgartner, and Stefan Wildermann. Hybrid Application Mapping for Composable Many-Core Systems: Overview and Future Perspective. Journal of Low Power Electronics and Applications, 10:1–37, 2020. [ DOI ] |

| [13] | M. Sagi, N. A. V. Doan, M. Rapp, T. Wild, J. Henkel, and A. Herkersdorf. A lightweight nonlinear methodology to accurately model multi-core processor power. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, pages 1–1, 2020. [ DOI ] |

| [14] |

Mark Sagi, Nguyen Anh Vu Doan, Nael Fasfous, Thomas Wild, and Andreas

Herkersdorf.

Fine-grained power modeling of multicore processors using ffnns.

In Alex Orailoglu, Matthias Jung, and Marc Reichenbach, editors,

Embedded Computer Systems: Architectures, Modeling, and Simulation, pages

186–199, Cham, 2020. Springer International Publishing.

To minimize power consumption while maximizing performance, today's multicore processors rely on fine-grained run-time dynamic power information – both in the time domain, e.g. $$\mu s$$μsto ms, and space domain, e.g. core-level. The state-of-the-art for deriving such power information is mainly based on predetermined power models which use linear modeling techniques to determine the core-performance/core-power relationship. However, with multicore processors becoming ever more complex, linear modeling techniques cannot capture all possible core-performance related power states anymore. Although, artificial neural networks (ANN) have been proposed for coarse-grained power modeling of servers with time resolutions in the range of seconds, no work has yet investigated fine-grained ANN-based power modeling. In this paper, we explore feed-forward neural networks (FFNNs) for core-level power modeling with estimation rates in the range of 10 kHz. To achieve a high estimation accuracy, we determine optimized neural network architectures and train FFNNs on performance counter and power data from a complex-out-of-order processor architecture. We show that, relative power estimation error decreases on average by 7.5% compared to a state-of-the-art linear power modeling approach and decreases by 5.5% compared to a multivariate polynomial regression model. Furthermore, we propose an implementation for run-time inference of the power modeling FFNN and show that the area overhead is negligible. |

| [15] | Mark Sagi, Nguyen Anh Vu Doan, Thomas Wild, and Andreas Herkersdorf. Multicore Power Estimation using Independent Component Analysis based Modeling. In 2019 IEEE 13th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), October 2019. |

| [16] | Andreas Herkersdorf. As embedded systems became serious grown-ups, they decide on their own. Invited Talk at the Workshop on Embedded Systems, Dedicated to Peter Marwedel on the Occasion of his 70th Birthday, Dortmund, July 4, 2019. |

| [17] | Hussam Amrouch, Heba Khdr, and Jörg Henkel. Aging effects: From physics to CAD. In Harnessing Performance Variability in Embedded and High-performance Many/Multi-core Platforms, pages 43–69. Springer, 2019. |

| [18] | Martin Rapp, Hussam Amrouch, Marilyn Wolf, and Jörg Henkel. Machine learning techniques to support many-core resource management: Challenges and opportunities. In 2019 ACM/IEEE 1st Workshop on Machine Learning for CAD (MLCAD), pages 1–6. IEEE, 2019. |

| [19] | Martin Rapp, Sami Salamin, Hussam Amrouch, Girish Pahwa, Yogesh Chauhan, and Jörg Henkel. Performance, power and cooling trade-offs with NCFET-based many-cores. In Design Automation Conference (DAC), page 41. ACM, 2019. |

| [20] | Martin Rapp, Anuj Pathania, Tulika Mitra, and Jörg Henkel. Prediction-based task migration on S-NUCA many-cores. In Design, Automation & Test in Europe (DATE), pages 1579–1582. IEEE, 2019. |

| [21] | Jörg Henkel, Heba Khdr, and Martin Rapp. Smart thermal management for heterogeneous multicores. In Design, Automation & Test in Europe (DATE), pages 132–137. IEEE, 2019. |

| [22] | Sami Salamin, Martin Rapp, Hussam Amrouch, Girish Pahwa, Yogesh Chauhan, and Jörg Henkel. NCFET-aware voltage scaling. In International Symposium on Low Power Electronics and Design (ISLPED). IEEE, 2019. |

| [23] | Heba Khdr, Hussam Amrouch, and Jorg Henkel. Dynamic Guardband Selection: Thermal-Aware Optimization for Unreliable Multi-Core Systems. Transactions on Computers (TC), 2019. |

| [24] | Anuj Pathania and Jörg Henkel. HotSniper: Sniper-Based Toolchain for Many-Core Thermal Simulations in Open Systems. Embedded Systems Letters (ESL), 2019. |

| [25] | Behnaz Pourmohseni, Fedor Smirnov, Heba Khdr, Stefan Wildermann, Jürgen Teich, and Jörg Henkel. Thermally composable hybrid application mapping for real-time applications in heterogeneous many-core systems. In Proceedings of the 40th IEEE Real-Time Systems Symposium (RTSS), 2019. [ DOI ] |

| [26] | Jörg Henkel, Jürgen Teich, Stefan Wildermann, and Hussam Amrouch. Dynamic resource management for heterogeneous many-cores. In Proceedings of the International Conference on Computer-Aided Design (ICCAD), pages 60:1–60:6. ACM, November 2018. [ DOI ] |

| [27] | Jörg Henkel. Power density and circuit aging – system-level means for mitigation. Keynote, IEEE Computer Society Annual Symposium on VLSI, Hong Kong, July 2018. |

| [28] | Anuj Pathania, Heba Khdr, Muhammad Shafique, Tulika Mitra, and Jörg Henkel. Qos-aware stochastic power management for many-cores. In 55th ACM/EDAC/IEEE Design Automation Conference (DAC 2018), June 2018. |

| [29] | Heba Khdr, Hussam Amrouch, and Jörg Henkel. Aging-constrained performance optimization for multi cores. In 55th ACM/EDAC/IEEE Design Automation Conference (DAC 2018), June 2018. |

| [30] | Heba Khdr. Resource Management for Multicores to Optimize Performance under Temperature and Aging Constraints. Dissertation, Chair of Embedded Systems, Department of Informatics, Karlsruhe Institute of Technology, Germany, 2018. |

| [31] | Santiago Pagani, Jian-Jia Chen, Muhammad Shafique, and Jörg Henkel. Advanced Techniques for Power, Energy, and Thermal Management for Clustered Manycores. Springer, 2018. |

| [32] | Santiago Pagani, Sai Manoj PD, Axel Jantsch, and Jörg Henkel. Machine Learning for Power, Energy, and Thermal Management on Multi-core Processors: A Survey. Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2018. |

| [33] | Martin Rapp, Anuj Pathania, and Jörg Henkel. Pareto-optimal power- and cache-aware task mapping for many-cores with distributed shared last-level cache. In International Symposium on Low Power Electronics and Design (ISLPED). IEEE, 2018. |

| [34] | Vanchinathan Venkatramani, Anuj Pathania, Muhammad Shafique, Tulika Mitra, and Jörg Henkel. Scalable dynamic task scheduling on adaptive many-core (invited). In 12th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC). IEEE, 2018. |

| [35] | Anuj Pathania and Jörg Henkel. Task scheduling for many-cores with s-nuca caches. In Proceedings of Design, Automation & Test in Europe Conference & Exhibition (DATE), pages 557–562. IEEE, 2018. |

| [36] | Heba Khdr, Hussam Amrouch, and Jörg Henkel. Aging-aware boosting. IEEE Transactions on Computers (TC), 2018. [ DOI ] |

| [37] | Heba Khdr, Santiago Pagani, Muhammad Shafique, and Jörg Henkel. Dark silicon aware resource management for many-core systems. In Advances in Computers: Dark Silicon and Future of On-chip Systems. Elsevier, 2018. |

| [38] | Anuj Pathania. Scalable Task Schedulers for Many-Core Architectures. Dissertation, Chair of Embedded Systems, Department of Informatics, Karlsruhe Institute of Technology, Germany, 2018. |

| [39] | Jörg Henkel. The triangle of power density, circuit degradation and reliability. Invited Keynote Speech, 30th IEEE International System-On-Chip Conference (SoCC 2017), Munich, Germany, September 7, 2017. |

| [40] | Santiago Pagani, Muhammad Shafique, and Jörg Henkel. Design space exploration and run-time adaptation for multi-core resource management under performance and power constraints. In Soonhoi Ha and Jürgen Teich, editors, Handbook of Hardware/Software Codesign, volume 1, pages 301–332. Springer, September 2017. [ DOI ] |

| [41] | Anuj Pathania, Heba Khdr, Muhammad Shafique, Tulika Mitra, and Jörg Henkel. Distributed scheduling for many-cores using cooperative game theory. In Design Automation and Test in Europe (DATE), March 2017. |

| [42] | Heba Khdr, Santiago Pagani, Éricles R. Sousa, Vahid Lari, Anuj Pathania, Frank Hannig, Muhammad Shafique, Jürgen Teich, and Jörg Henkel. Power density-aware resource management for heterogeneous tiled multicores. IEEE Transactions on Computers (TC), 66(3):488–501, March 1, 2017. [ DOI ] |

| [43] | Anuj Pathania, Heba Khdr, Muhammad Shafique, Tulika Mitra, and Jörg Henkel. Scalable probabilistic power budgeting for many-cores. In Proceedings of Design, Automation and Test in Europe Conference Exhibition (DATE). IEEE, 2017. |

| [44] | Philipp Wagner, Thomas Wild, and Andreas Herkersdorf. Diasys: Improving soc insight through on-chip diagnosis. Journal of Systems Architecture, 2017. [ DOI ] |

| [45] | Santiago Pagani, Anuj Pathania, Muhammad Shafique, Jian-Jia Chen, and Jörg Henkel. Energy efficiency for clustered heterogeneous multicores. IEEE Transactions on Parallel and Distributed Systems (TPDS), 28(5):1315–1330, 2017. [ DOI ] |

| [46] | Santiago Pagani, Heba Khdr, Jian-Jia Chen, Muhammad Shafique, Minming Li, and Jörg Henkel. Thermal safe power (TSP): Efficient power budgeting for heterogeneous manycore systems in dark silicon. IEEE Transactions on Computers (TC), 66(1):147–162, 2017. Feature Paper of the Month. [ DOI ] |

| [47] | Santiago Pagani, Heba Khdr, Jian-Jia Chen, Muhammad Shafique, Minming Li, and Jörg Henkel. Thermal safe power: Efficient thermal-aware power budgeting for manycore systems in dark silicon. In Amir M. Rahmani, Pasi Liljeberg, Ahmed Hemani, Axel Jantsch, and Hannu Tenhunen, editors, The Dark Side of Silicon. Springer, 2017. |

| [48] |

P. Wagner, L. Li, T. Wild, A. Mayer, and A. Herkersdorf.

What happens on an mpsoc stays on an mpsoc - unfortunately!

In 2016 International Symposium on Integrated Circuits (ISIC),

pages 1–2, December 2016.

[ DOI ]

Keywords: hardware-software codesign;microprocessor chips;program diagnostics;program testing;system-on-chip;MPSoC;hardware-software systems;multiprocessor system-on-chip;on-chip observations;software diagnosis;Bandwidth;Computer bugs;Hardware;Linux;Observability;Software;System-on-chip |

| [49] | Santiago Pagani. Power, Energy, and Thermal Management for Clustered Manycores. Dissertation, Chair for Embedded Systems (CES), Department of Computer Science, Karlsruhe Institute of Technology (KIT), Germany, November 24, 2016. Received Summa cum Laude and the ACM SIGBED Paul Caspi Memorial Dissertation Award. [ DOI ] |

| [50] | Santiago Pagani, Lars Bauer, Qingqing Chen, Elisabeth Glocker, Frank Hannig, Andreas Herkersdorf, Heba Khdr, Anuj Pathania, Ulf Schlichtmann, Doris Schmitt-Landsiedel, Mark Sagi, Éricles Sousa, Philipp Wagner, Volker Wenzel, Thomas Wild, and Jörg Henkel. Dark silicon management: An integrated and coordinated cross-layer approach. it – Information Technology, 58(6):297–307, September 16, 2016. [ DOI ] |

| [51] | Anas Toma, Santiago Pagani, Jian-Jia Chen, Wolfgang Karl, and Jörg Henkel. An energy-efficient middleware for computation offloading in real-time embedded systems. In 22nd IEEE International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA), August 2016. |

| [52] | Mark Sagi and Andreas Herkersdorf. On-chip diagnosis of multicore platforms for power management. Workshop Presentation, DTC 2016, The Munich Workshop on Design Technology Coupling, Munich, Germany, June 30, 2016. |

| [53] | Ravi Kumar Pujari, Thomas Wild, and Andreas Herkersdorf. Tcu: A multi-objective hardware thread mapping unit for hpc clusters. In M. Julian Kunkel, Pavan Balaji, and Jack Dongarra, editors, High Performance Computing: 31st International Conference, ISC High Performance 2016, Frankfurt, Germany, June 19-23, 2016, Proceedings, pages 39–58. Springer International Publishing, June 2016. [ DOI ] |

| [54] | Jörg Henkel, Santiago Pagani, Heba Khdr, Florian Kriebel, Semeen Rehman, and Muhammad Shafique. Towards performance and reliability-efficient computing in the dark silicon era. In Proceedings of the 19th Design, Automation and Test in Europe (DATE), March 2016. |

| [55] | Philipp Wagner, Thomas Wild, and Andreas Herkersdorf. Diasys: On-chip trace analysis for multi-processor system-on-chip. In Architecture of Computing Systems (ARCS'16). Springer, 2016. |

| [56] | Hans Michael Gerndt, Michael Glaß, Sri Parameswaran, and Barry L. Rountree. Dark Silicon: From Embedded to HPC Systems (Dagstuhl Seminar 16052). Dagstuhl Reports, 6(1):224–244, 2016. [ DOI ] |

| [57] | Muhammad Usman Karim Khan. Towards Computational Efficiency of Next Generation Multimedia Systems. Dissertation, Chair for Embedded Systems (CES), Department of Computer Science, Karlsruhe Institute of Technology (KIT), Germany, December 21, 2015. |

| [58] | Santiago Pagani, Jian-Jia Chen, Muhammad Shafique, and Jörg Henkel. Thermal-aware power budgeting for dark silicon chips. In Proceedings of the 2nd Workshop on Low-Power Dependable Computing (LPDC) at the International Green and Sustainable Computing Conference (IGSC), December 2015. |

| [59] | M. Shafique and J. Henkel. Mitigating power density and temperature problems in the nano-era. In IEEE/ACM 34th International Conference on Computer-Aided Design (ICCAD), November 2, 2015. Special Session Paper. |

| [60] | R. K. Pujari, T. Wild, and A. Herkersdorf. A hardware-based multi-objective thread mapper for tiled manycore architectures. In Computer Design (ICCD), 2015 33rd IEEE International Conference on, pages 459–462, October 2015. [ DOI ] |

| [61] | Santiago Pagani, Muhammad Shafique, Heba Khdr, Jian-Jia Chen, and Jörg Henkel. seBoost: Selective boosting for heterogeneous manycores. In 10th IEEE/ACM International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), pages 104–113, October 2015. [ DOI ] |

| [62] | Jörg Henkel. Dark silicon and dependability. Keynote Talk, International Symposium on Computer Architecture & Digital Systems (CADS), October 8, 2015. |

| [63] | Santiago Pagani, Jian-Jia Chen, and Jörg Henkel. Energy and peak power efficiency analysis for the single voltage approximation (SVA) scheme. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 34(9):1415–1428, September 2015. [ DOI ] |

| [64] | J. Henkel, H. Bukhari, S. Garg, M. U. K. Khan, H. Khdr, F. Kriebel, U. Ogras, S. Parameswaran, and M. Shafique. Dark silicon - from computation to communication. In International Symposium on Networks-on-Chip (NOCS), September 2015. Invited Special Session Paper. |

| [65] | Andreas Herkersdorf. What happens on an MPSoC stays on an MPSoC unfortunately! Keynote Talk at MPSoC Forum, July 13, 2015. |

| [66] | A. Pathania, S. Pagani, M. Shafique, and J. Henkel. Power management for mobile games on asymmetric multi-cores. In ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED), pages 243–248, July 2015. [ DOI ] |

| [67] | M. U. K. Khan, M. Shafique, and J. Henkel. Hierarchical power budgeting for dark silicon chips. In ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED), pages 213–218, July 2015. [ DOI ] |

| [68] | Santiago Pagani, Muhammad Shafique, Jian-Jia Chen, and Jörg Henkel. Thermal-aware power budgeting for dark silicon chips (invited talk). In Workshop on System-to-Silicon Performance Modeling and Analysis at the 52nd ACM/EDAC/IEEE Design Automation Conference (DAC), June 2015. |

| [69] | H. Khdr, S. Pagani, M. Shafique, and J. Henkel. Thermal constrained resource management for mixed ilp-tlp workloads in dark silicon chips. In 52nd Design Automation Conference (DAC), pages 179:1–179:6. ACM, June 2015. HiPEAC Paper Award. [ DOI ] |

| [70] | M. U. K. Khan, M. Shafique, and J. Henkel. Hardware-software co-design for next generation dark silicon multimedia systems. Ph.D. Forum at the ACM/EDAC/IEEE 52nd Design Automation Conference (DAC), June 2015. |

| [71] | J. Henkel, H. Khdr, S. Pagani, and M. Shafique. New trends in dark silicon. In Proceedings of the 52nd ACM/EDAC/IEEE Design Automation Conference (DAC), pages 119:1–119:6. ACM, June 2015. HiPEAC Paper Award. [ DOI ] |

| [72] | D. Gnad, M. Shafique, F. Kriebel, S. Rehman, D. Sun, and J. Henkel. Hayat: Harnessing dark silicon and variability for aging deceleration and balancing. In 52nd Design Automation Conference (DAC), pages 180:1–180:6, June 2015. HiPEAC Paper Award. [ DOI ] |

| [73] | Philipp Wagner, Lin Li, Thomas Wild, Albrecht Mayer, and Andreas Herkersdorf. Knowledge-Based On-Chip Diagnosis for Multi-Core Systems-on-Chip. In edaWorkshop 15, pages 39–45, Dresden, Germany, May 2015. |

| [74] | Jörg Henkel, Muhammad Usman Karim Khan, and Muhammad Shafique. Energy-efficient multimedia systems for high efficiency video coding. In IEEE International Symposium on Circuits and Systems (ISCAS), May 2015. (accepted as a reviewed Special Session paper). |

| [75] | Muhammad Shafique, Dennis Gnad, Siddharth Garg, and Jörg Henkel. Variability-aware dark silicon management in on-chip many-core systems. In 18th IEEE/ACM Design, Automation and Test in Europe (DATE), March 2015. |

| [76] | Muhammad Shafique. Run-time resource and reliability management in dark silicon many-core chips. Keynote Talk, International Workshop on Multi-Objective Many-Core Design (MOMAC), March 2015. |

| [77] | Santiago Pagani, Jian-Jia Chen, Muhammad Shafique, and Jörg Henkel. MatEx: Efficient transient and peak temperature computation for compact thermal models. In 18th Design, Automation and Test in Europe (DATE), pages 1515–1520, March 2015. [ DOI ] |

| [78] | M. U. K. Khan, M. Shafique, and J. Henkel. Hardware-software co-design for next generation dark silicon multimedia systems. Ph.D. Forum at the IEEE/ACM 16th Design Automation and Test in Europe Conference (DATE). Ph.D. Forum Best Poster Award, March 2015. |

| [79] | M. Shafique and S. Rehman. Designing and architecting advanced embedded systems. Tutorial at National University of Sciences and Technology (NUST), December 2014. |

| [80] | Waqaas Munawar, Heba Khdr, Santiago Pagani, Muhammad Shafique, Jian-Jia Chen, and Jörg Henkel. Peak power management for scheduling real-time tasks on heterogeneous many-core systems. In 20th IEEE International Conference on Parallel and Distributed Systems (ICPADS), December 2014. |

| [81] | Felipe Sampaio, Muhammad Shafique, Bruno Zatt, Sergio Bampi, and Jörg Henkel. Energy-efficient architecture for advanced video memory. In IEEE/ACM 33rd International Conference on Computer-Aided Design (ICCAD), November 2014. |

| [82] | Muhammad Shafique. Application-driven power management for on-chip memories. Invited Talk at Memory Architecture and Organization Workshop (MeAOW) at ESWeek, October 16, 2014. |

| [83] | Muhammad Shafique, Muhammad Usman Karim Khan, and Jörg Henkel. Power efficient and workload balanced tiling for parallelized high efficiency video coding. In 21st IEEE International Conference on Image Processing (ICIP), October 2014. |

| [84] | Muhammad Shafique, Siddharth Garg, Tulika Mitra, Sri Parameswaran, and Jörg Henkel. Dark silicon as a challenge for hardware/software co-design: Invited special session paper. In IEEE/ACM International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), October 2014. [ DOI ] |

| [85] | Santiago Pagani, Heba Khdr, Waqaas Munawar, Jian-Jia Chen, Muhammad Shafique, Minming Li, and Jörg Henkel. TSP: Thermal safe power - efficient power budgeting for many-core systems in dark silicon. In 9th IEEE/ACM International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), pages 10:1–10:10, October 2014. Best Paper Award. [ DOI ] |

| [86] | Jörg Henkel. Dependability of on-chip systems in the dark silicon era. Keynote Talk, 32nd IEEE International Conference on Computer Design (ICCD), October 2014. |

| [87] | Felipe Sampaio, Muhammad Shafique, Bruno Zatt, Sergio Bampi, and Jörg Henkel. Content-driven memory pressure balancing and video memory power management for parallel high efficiency video coding. In ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED), August 2014. [ DOI ] |

| [88] | Muhammad Shafique, Siddharth Garg, Jörg Henkel, and Diana Marculescu. The eda challenges in the dark silicon era: Temperature, reliability, and variability perspectives. In 51st Design Automation Conference (DAC), June 2014. [ DOI ] |

| [89] | M. U. K. Khan, M. Shafique, and J. Henkel. Application-specific hierarchical power management for multicast high efficiency video coding. In ACM/EDAC/IEEE 51st Design Automation Conference (DAC), June 2014. Designer Track Best Poster Award. |

| [90] | Jörg Henkel. The dark silicon problem in multi-core systems – invasive computing as a solution. Keynote Talk, Thematic Session at HiPEAC Computer Systems Week, May 13, 2014. |

| [91] | F. Sampaio, M. Shafique, B. Zatt, S. Bampi, and J. Henkel. dsvm: Energy-efficient distributed scratchpad video memory architecture for the next-generation high efficiency video coding. In Design, Automation and Test in Europe (DATE), March 2014. [ DOI ] |

| [92] | Muhammad Usman Karim Khan, Muhammad Shafique, and Jörg Henkel. Software architecture of high efficiency video coding for many-core systems with power-efficient workload balancing. In Design, Automation and Test in Europe (DATE), March 2014. [ DOI ] |

| [93] | Muhammad Shafique and Jörg Henkel. Low power design of the next-generation high efficiency video coding. In 19th Asia and South Pacific Design Automation Conference (ASP-DAC), pages 274–281, January 2014. [ DOI ] |

| [94] | Muhammad Shafique, Lars Bauer, and Jörg Henkel. Adaptive energy management for dynamically reconfigurable processors. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 33(1):50–63, January 2014. [ DOI ] |

| [95] | Santiago Pagani and Jian-Jia Chen. Energy efficient task partitioning based on the single frequency approximation scheme. In Proceedings of the 34th IEEE Real-Time Systems Symposium (RTSS), pages 308–318, December 2013. [ DOI ] |

| [96] | Muhammad Shafique and Jörg Henkel. Agent-based distributed power management for kilo-core processors. In IEEE/ACM International Conference on Computer-Aided Design (ICCAD), pages 153–160, November 2013. |

| [97] | Muhammad Usman Karim Khan, Muhammad Shafique, and Jörg Henkel. Amber: Adaptive energy management for on-chip hybrid video memories. In IEEE/ACM International Conference on Computer-Aided Design (ICCAD), pages 405–412, November 2013. |

| [98] | Santiago Pagani and Jian-Jia Chen. Energy efficiency analysis for the single frequency approximation (SFA) scheme. In Proceedings of the 19th IEEE International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA), pages 82–91, August 2013. Best Paper Award. [ DOI ] |

| [99] | Bruno Zatt, Muhammad Shafique, Sergio Bampi, and Jörg Henkel. 3d video coding for embedded devices: Energy efficient algorithms and architectures. In Springer Science+Business Media, LLC, May 2013. |

| [100] | Muhammad Shafique, Benjamin Vogel, and Jörg Henkel. Self-adaptive hybrid dynamic power management for many-core systems. In Proceedings of Design, Automation and Test in Europe Conference (DATE), pages 51–56, March 2013. [ DOI ] |

| [101] | Felipe Sampaio, Bruno Zatt, Muhammad Shafique, Luciano Agostini, Sergio Bampi, and Jörg Henkel. Energy-efficient memory hierarchy for motion and disparity estimation in multiview video coding. In Proceedings of Design, Automation and Test in Europe Conference (DATE), pages 665–670, March 2013. [ DOI ] |

| [102] | Jörg Henkel, Andreas Herkersdorf, Lars Bauer, Thomas Wild, Michael Hübner, Ravi Kumar Pujari, Artjom Grudnitsky, Jan Heisswolf, Aurang Zaib, Benjamin Vogel, Vahid Lari, and Sebastian Kobbe. Invasive manycore architectures. In Proceedings of the 17th Asia and South Pacific Design Automation Conference (ASP-DAC), pages 193–200, January 2012. [ DOI ] |

| [103] | Ravi Kumar Pujari, Thomas Wild, Andreas Herkersdorf, Benjamin Vogel, and Jörg Henkel. Hardware assisted thread assignment for RISC based MPSoCs in invasive computing. In Proceedings of the 13th International Symposium on Integrated Circuits (ISIC), pages 106–109, December 2011. [ DOI ] |

| [104] | Muhammad Shafique. Architectures for Adaptive Low-Power Embedded Multimedia Systems. Dissertation, Chair for Embedded Systems (CES), Department of Computer Science, Karlsruhe Institute of Technology (KIT), Germany, January 31, 2011. |

| [105] | Jürgen Teich, Jörg Henkel, Andreas Herkersdorf, Doris Schmitt-Landsiedel, Wolfgang Schröder-Preikschat, and Gregor Snelting. Invasive computing: An overview. In Michael Hübner and Jürgen Becker, editors, Multiprocessor System-on-Chip – Hardware Design and Tool Integration, pages 241–268. Springer, Berlin, Heidelberg, 2011. [ DOI ] |

| [106] | G. Frantz, J. Henkel, J. Rabaey, T. Schneider, M. Wolf, and U. Batur. Ultra-low power signal processing. IEEE Signal Processing Magazine, 27(2):149–154, 2010. [ DOI ] |

| [107] | Jürgen Teich. Invasive algorithms and architectures. it - Information Technology, 50(5):300–310, 2008. |

| [108] | Naehyuck Chang and Jörg Henkel. Guest editorial: Current trends in low-power design. ACM Transactions on Design Automation of Electronic Systems (TODAES), 16:1:1–1:8. [ DOI ] |